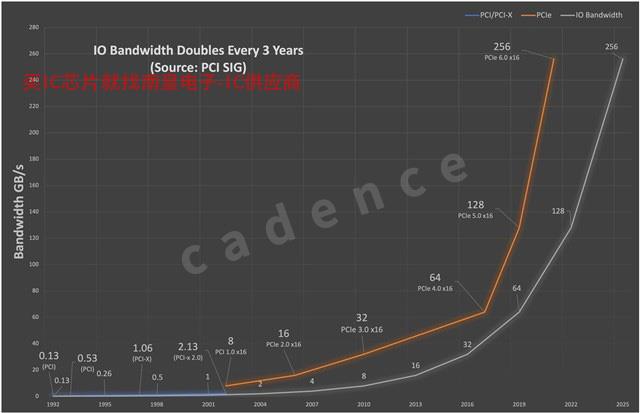

����ʽ�l���ԁ���PCI Express��PCIe���S���F����������Ŀ��ٰlչ��������Ӌ�㡢�˹�����/�C���W����ML�����ò��ɻ�ȱ�ļ��g������������W�j�m�����̑B�惦�����H��ˣ�PCIeԓ���g������ٶȺ����t�����ͻ��Ҳ�V�������ڴ惦�ܘ������磬ͨ�^PCIe/CXL����B�ӵij־Ãȴ��DRAM����

оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

�˹�����/�C���W����ML�����ó����׃������I����ؓ�ɼ����w�Ƶ��ƶ˵�څ�ݣ��^�m�ƄӔ�������ǰ��δ�е����L�����˝M��δ�팦��������������PCI-SIG��2019��l����PCIe 6.��������ݔ���ʷ�����64GT/s����K��PCIe 6.2022��1��2��1����ʽ�l����

IO�������L�A�y��PCIe�˜���׃(�DƬ:Cadence��

PCIe 6.0����Ҫ����

��I/O������PCIe 5.0��32GT/s������64GT/s�o��̖�����ԣ�SI���������˾������PCIe�����ݵ��������^�m֧��PCB�����yͨ�������B���^�͔Uչ�����������ʞ�32GT/s�����ò��w���ƣ�NRZ�����a�r�����yͨ���IJ���p�Ŀ������ο�˹��(16GHz���¿��_��36dB���ϣ���������ߵ�64GT/s NRZ���ο�˹�ص��l�ʷ�����32GHz��ͨ���l�ʵ����P�pʧ�����ӵ�70dB���ϡ��@�Nȫͨ����̖�pʧ��ʹ����ȫ�o���R�e����ݔ�Ĕ���Ҳ�o����Ч�֏͡�

PAM4�ӳ�PCIe

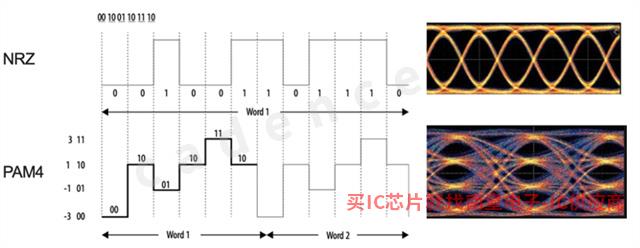

��̖�{��ģʽ�ķǚw�㾎�a��NRZ���Ğ����ƽ�}�_�����{�ƣ�PAM4����PCIe 6.�˷�ͨ����̖�pʧ����ķ�����PAM4��һ�N���ƽ��̖��ݔ���g��ÿ���g��UI����NRZÿ��λ�r�gֻ��ݔ1����(Ҋ�D2)������PAM4.��̖�{�Ƽ��gPCIe 6.0ÿ��UI���ο�˹���l�ʲ�׃����r�£����Ԃ�ݔ2���ؔ������������ʷ���PCIe 6.0��һ�ݡ���ˣ�ͨ���pʧҲ�S֮����PCIe 5.0һ�ӿɿء�

PAM4��̖�{��(�DƬ:Cadence��

���ǣ�����������PAM4��̖�{�Ƶ�PCIe�汾߀��Ҫ��Qһϵ�����𣬲��������s�Ե����������\���ǣ�Cadence��PAM4����İ��������2017�꣬Cadence��ͨ�^��Nusemi��˾��ُ�_ʼ�аl112Gb/s��PAM4���g�����죬Cadence�������MFinFET���c��112G/56G PAM4 SerDes IP�͑�ʹ���҂����I�ȹ�����IP�_�l���S��ɹ���оƬ�OӋ��

�f�h����Ч�ʶ���

PIPE���������Ľӿ�Ҳ������6.0�棬���t�Mһ�����͡�

PCIe 6.���؆�Ԫ��������0�˜ʣ�FLIT�����cPAM4�����ǰ��m�e��FEC����Ч�f��Ҋ���õ�����ؓ�d����Ч�f�{���ṩ���͵����t��

PCIeǰ��ͨ�^�ӑB�·�����͵��Ġ�B���F���ܡ����ڴ��^���У��ӑB�·�������ɔ_�������Ă�ݔ��PCIe 6.0����ȫ�µĵ��Ġ�BL0p�����������������������{���������ɔ_��������

Cadence�Jorjin������PCIe 6.0������IP��Q����

Cadence��PCIe PHY�Ϳ�������Q����(�D:Cadence��

Cadence���������I�ИI�������®aƷPCIe 6.0�˜ʣ���PCIe 6.0 IP����ǰ���I�����׃���ļ��g����Q�������^ȥ20�꣬Cadenceһֱ��PCIe PHY�I�ȵĹ����̺Ϳ�����������Cadence�I�ȵ�PAM����C�ļ��g��112G/56G PAM4��̫�WPHY IP���Y����PCIe�����I��Cadence�����ڞ��Ј��ṩ�����M�ķ���PCIe 6.0 PHY�Ϳ�����IP��

- 2022��̎�����Ј����m���ţ��֙C MPU �I��

- ���R���F��ͨ��˾Arriver��ͬ�_�l�Ԅ��{�ܛ����Q���������F�L�ڑ��Ժ���

- Codasip���l���£����M�n�̰lչ

- ����4750ϵ�ж�ܔ����������IEC�B����ģ�K

- ���_˹�l����ͣ����ؽM��ͻ�������W�j��14���C���c��

- ADI��Keysight������ �ӿ첿���ꇼ��g

- �����˹������~�����A�� YLearn����W���_Դ�Ŀ�ذ��l��

- MiR�����ƄәC���˰l���ˡ���܇�ИI�Ȳ��\ݔ�Ԅӻ�����Ƥ��

- �Q���_��Phoenix Contact���������B�������M��

- �ڕr��RF��͔��������{ԇ5G NR��ͨ��ϵ�y

- �_�e늡�늵��Ї��_���댧�w�����̌��L��ӡ��

- DisplayPort 2.0������DP40�cDP80�ɷN�J�C