AMD ���� 3D Chiplet �Y�����Ɍ��F3D ��ֱ���桱

��2025��9��3�ո��£�

6 �� 1 ����Ϣ �������_�� 2021 �_�����H��Xչ��Computex 2021���ϣ�AMD CEO �K���S�l���� 3D Chiplet ԓ���g�����ȑ����ڌ��F3D ��ֱ����(3D Vertical Cache����һЩ�߶ˮaƷ���ڽ������ǰ���a��

оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F؛�YԴ��оƬ��挍�r��ԃ���ИI�r���������ُ����ICоƬ�����Ȍ��IоƬ��ُƽ�_��

ԓ�ܘ���ԭ����ʽչʾNordic������3D Chiplet ��һ�� 64MB �� 7nm �� SRAM ֱ�ӶѯB��ÿ�����ďͺ��w�ϣ������ṩZen �������ĸ��� L3 ���������ӵ� 3 ����

3D ֱ�Ӿ���Zen 3���� CCD ͨ�^��ͨ���ڶѯBоƬ֮�g��ݔ��̖���ʣ�֧��ÿ�볬�^ 2TB �Ď�����

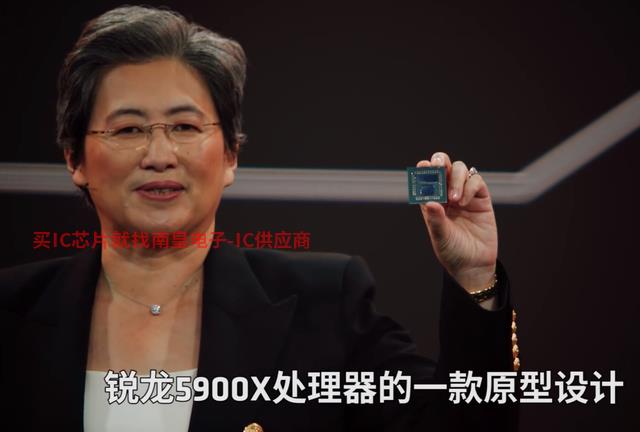

3D Chiplet �Y��̎������Ŀǰ���J�� 5000 ϵ�����^��ȫ��ͬ���ٷ�չʾ 3D Chiplet �ܘ����J�� 9 5900X ԭ��(�鷽��չʾ���ٷ����w)��

�K���S�f���ڌ��H�O���У�һ���Ϊ��� SRAM ���cÿһ�K CCD �Y�ϣ�ÿ�K CCD �������� 96MB�����چ����b�� 12 �˻� 16 �������ԫ@�ú�̎���� 192MB �ľ��档

���T�Pע����̖�����PƷ�ƣ�

�aƷ�c���ã�

ÿ�����^�l��

- ����̭��34���Ї���˾�Ĺ���机��O���ٴβ�ȡ�Єӣ��@���Ǿ��|��

- �����ѮaƷ�xʽ����߅���˹������cҕ�X��Blaize?, Inc.���߅���˹�����̎�����ߪ�

- ���8Gen1.���ؚvʷ�ĽK�Y���ɿ�����9000�֙C�Q��������ǰʮ

- ������WAR-Meta�����Rȫ���W�y�������״Ό��F

- ��˹���Ƴ������ܸ�����ȫ�� Licity? ճ�τ������ڹ躬�����^20%��ؓ�O����

- չ���YӍ|���y�ԏ�ȫ���aƷ�����P��Q��������CITE2022

- �˹����ܞ����늙C����Ч�ʎ������µ�˼·

- 2022 EdgeX�Ї�����ِ��ʽ�_Ļ��Ӣ�ؠ����ИI��������������߅������

- �������ǘsҫMagic V���F���MWi-Fi 6����

- FDA903��FDA803:���H��D����l�Ŵ�����߀�ܴ��������|

- �ɹ����������� ܇�d��܇ӛ䛃x���·���o

- ��˹�����ĆT��ȥ����������еĴ������߀����늄���܇������һЩ��ȥ���O�����R�d

оƬ��ُ�W��ע���χ������ڙ�IC�����̵ĬF؛�YԴ���p�ɲ�ُICоƬ���LJ��Ȍ��I��оƬ��ُƽ�_